[ad_1]

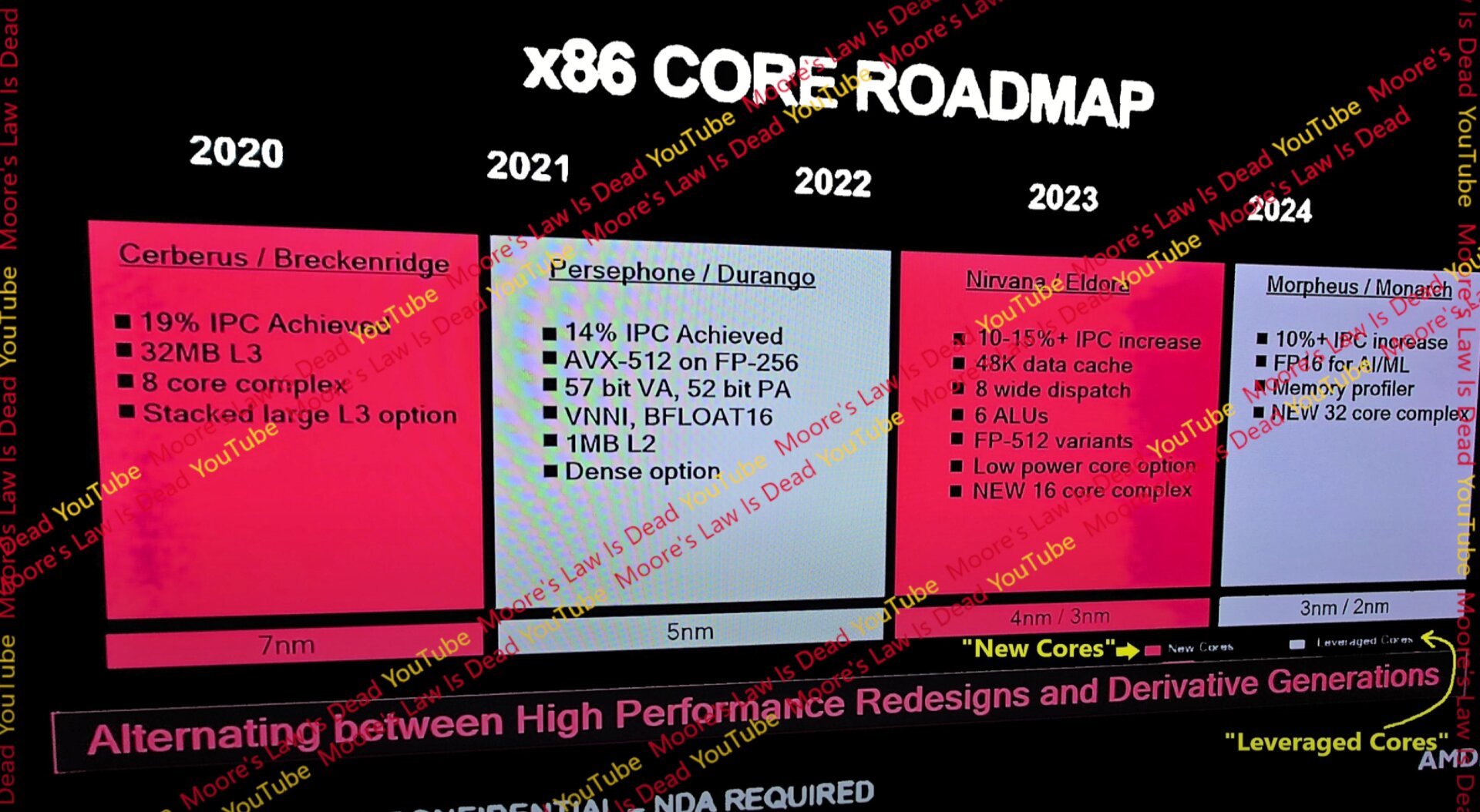

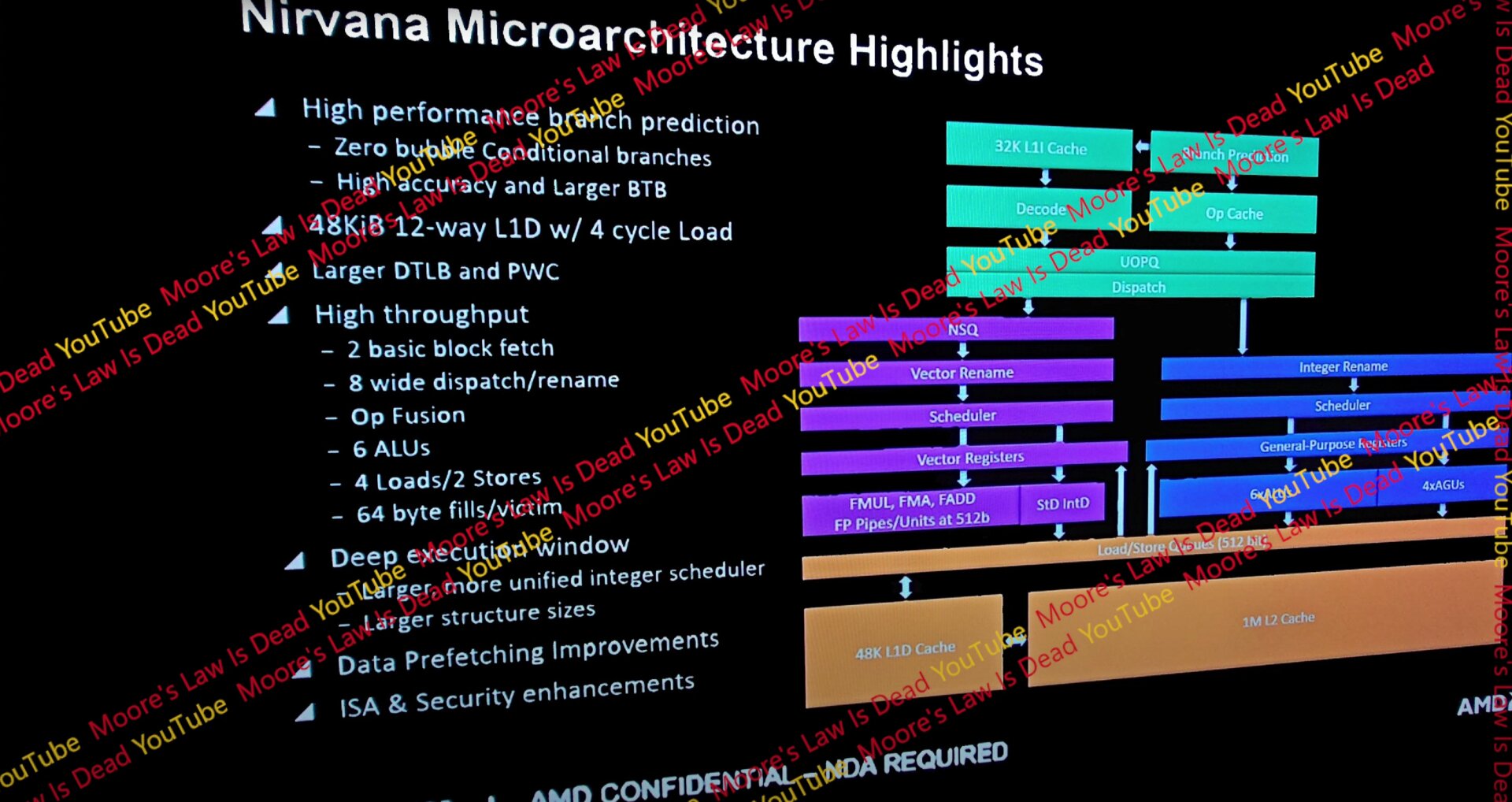

From an internal AMD presentation, more precisely a “design status update for EPYC“, is said to be a roadmap that provides information about the upcoming Zen 5 and Zen 6 architectures. There is also a diagram of Nirvana architecture (Zen 5).

Neither the authenticity nor the age of the presentation slides can be determined on the YouTube channel Moore’s Law is Dead published and, according to his own statements, optically changed it to protect the source. The information should therefore be treated with caution.

At the latest since looking at the LinkedIn profile of an AMD employee, it has been known that that Zen 5’s microarchitecture is codenamed Nirvanawhile his successor is Morpheus (Zen 6).

Information about the Zen 5 architecture (Nirvana)

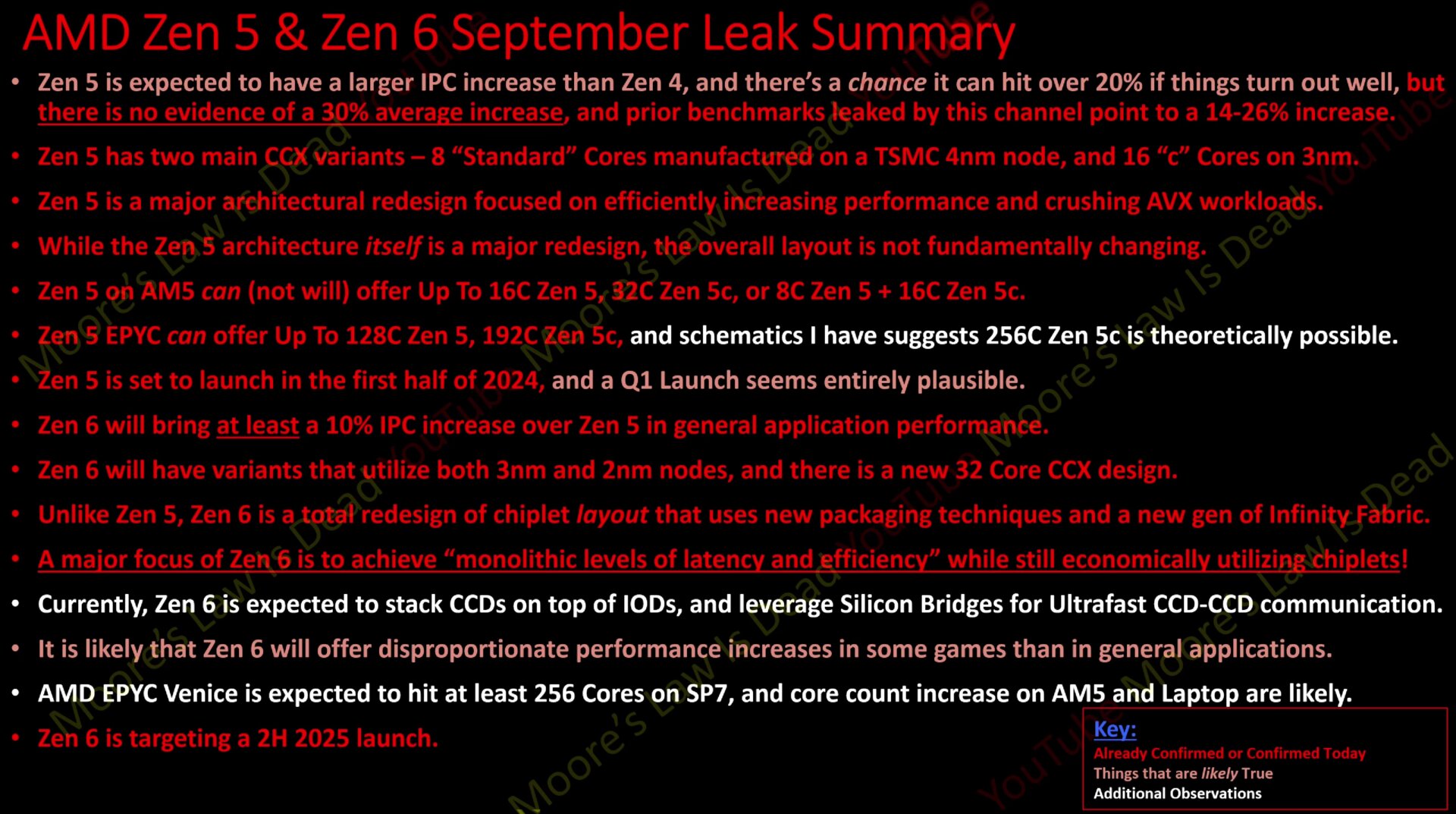

According to the roadmap, Nirvana is targeting an increase in instructions per clock cycle (IPC) in the range of 10 to 15 percent. Based on an earlier, albeit equally unconfirmed, Cinebench benchmark, the channel assumes a larger increase. At least the IPC should increase to a greater extent than was the case when switching from Zen 3 to Zen 4 with 14 percent (according to the roadmap). However, IPC information is generally difficult because ultimately it always depends on the viewing angle or the application.

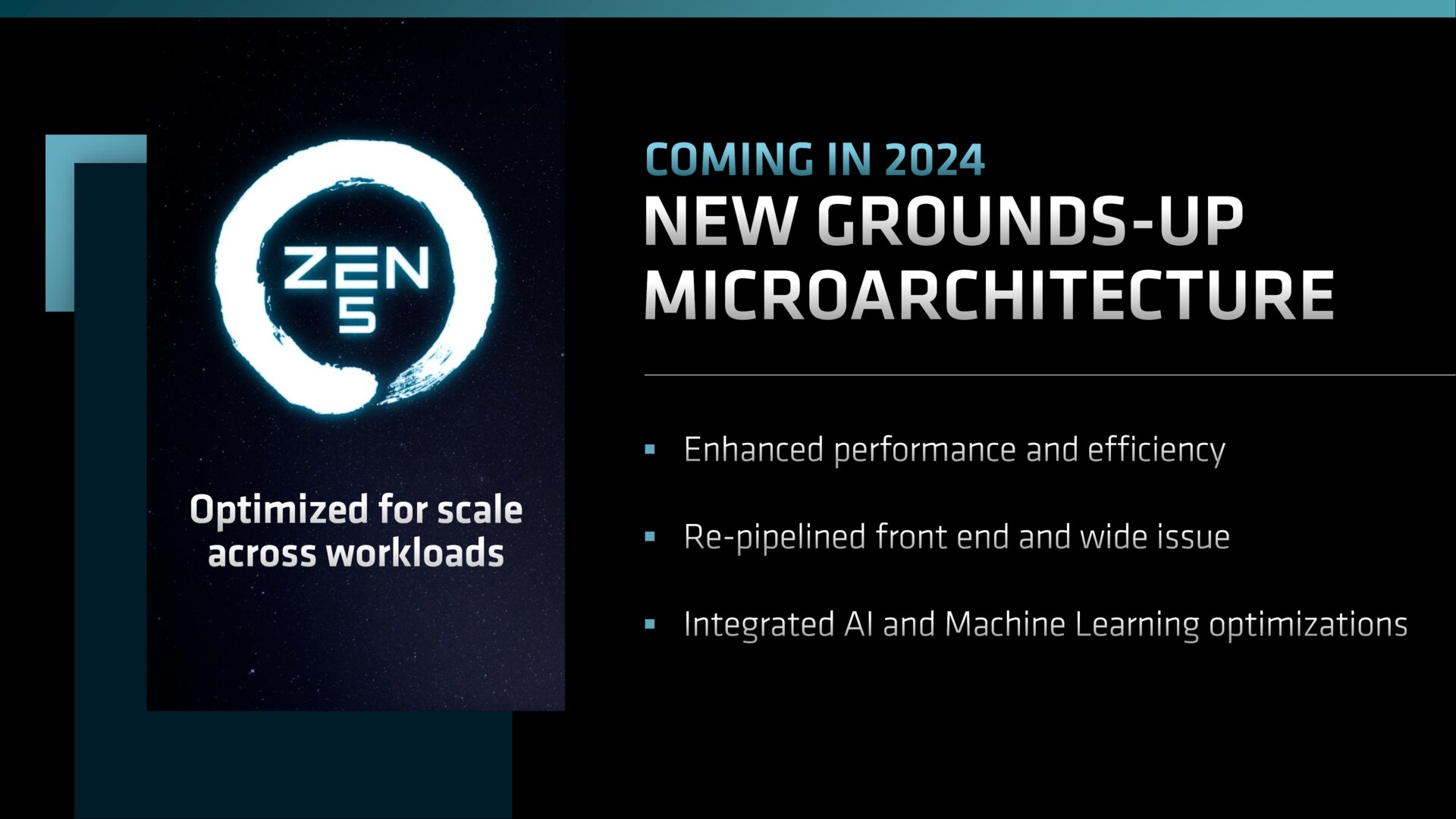

While Zen 4 was just an update of Zen 3 with comparatively small changes, Zen 5 is said to be a completely new microarchitecture, as AMD itself put it.

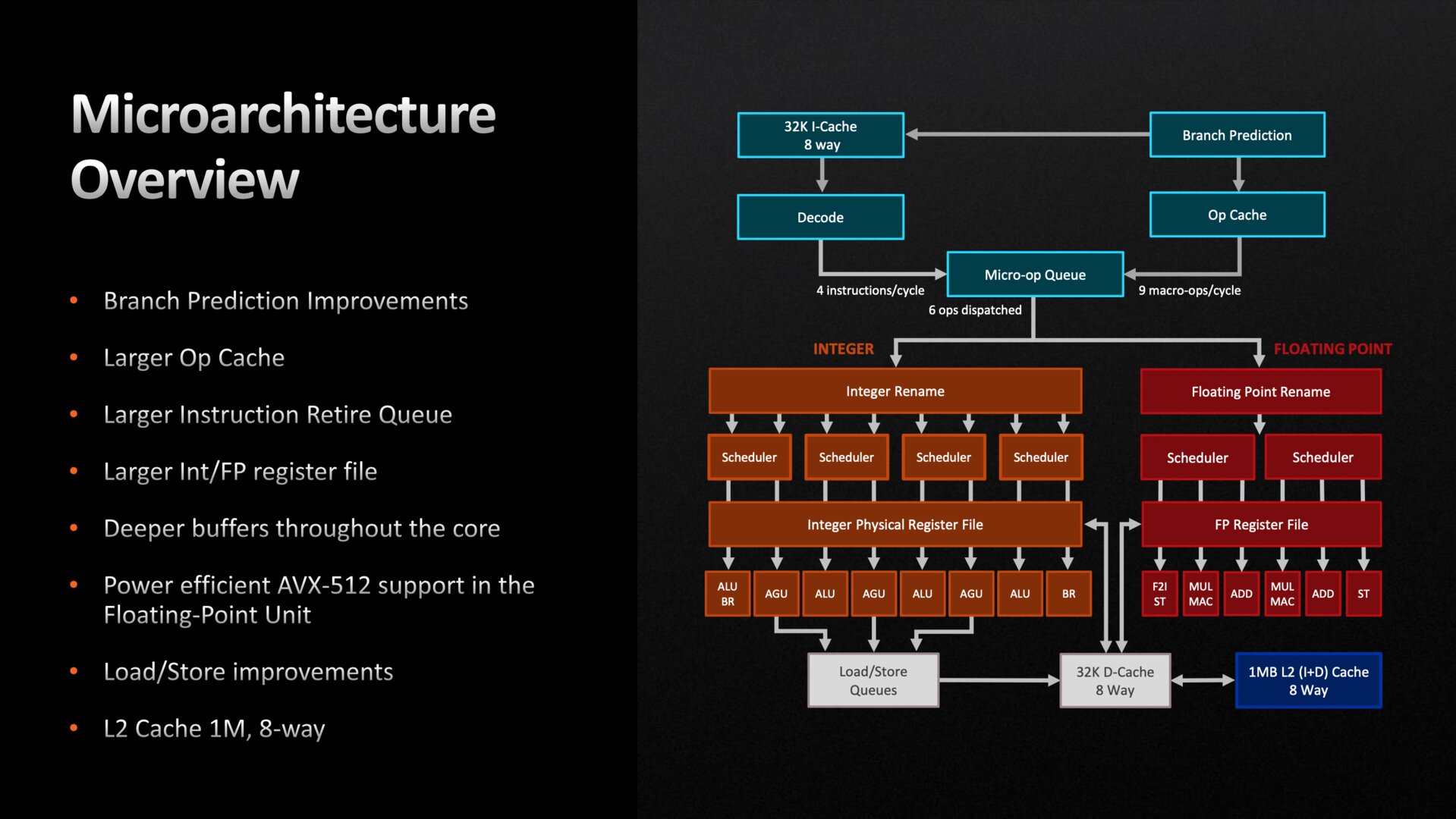

If the information in the roadmap is correct, a lot will change. The L1 data cache is to be increased from 32 KB to 48 KB and the number of ALUs should increase from 4 to 6 and thus also by 50 percent. However, the L2 cache remains unchanged at 1 MB per core.

Furthermore, there are FP-512 variants and a “Low power core option” the speech. Zen 5 will now have up to 16 active cores per Core Complex (CCX), doubling the number compared to Zen 4. In this context, it is unlikely that the smaller “c” cores are meant here, as they are in Zen 4c (Bergamo, Siena), because this option already exists in the predecessor and would therefore not be “new”.

However, the roadmap may not be up to date on this point, so Zen 4c is omitted and the 16-core CCX means Zen 5c. Both upcoming APUs from the Strix Point series becomes AMD will probably combine full-fledged Zen 5 cores with smaller Zen 5c cores.

Moore’s Law is Dead (MLID) also assumes that, like its predecessor, there will be a CCX with 8 large cores and a CCX with 16 small “c” cores.

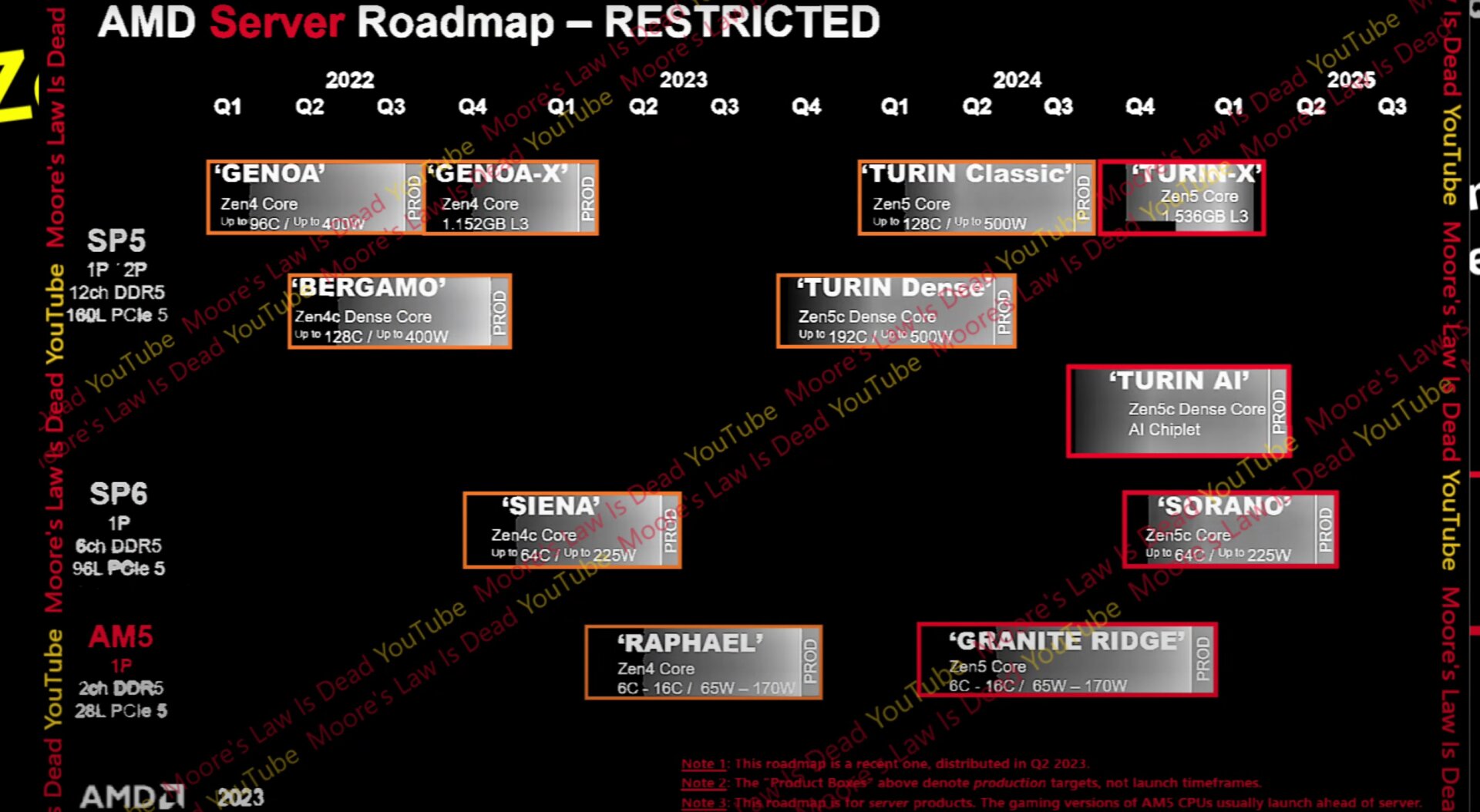

The channel had previously published another roadmap with equally unconfirmed data on upcoming server processors from AMD. There is talk of up to 128 Zen 5 cores in Turin, the successor to Genoa, and 192 Zen 5c cores in “Turin Dense”, the successor to Bergamo.

Information about Zen 6 (Morpheus)

There should only be a small jump from Zen 5 to Zen 6 (codename Morpheus). The very early and therefore rough forecast is that the IPC will increase by at least 10 percent. In addition, a 32-core CCX is mentioned for the first time. There is also talk of a memory profiler and FP16 commands for AI and machine learning.

For Zen 6, MLID expects a new layout with new packaging techniques and a new generation of Infinity Fabric. The channel is not yet so sure that the CPU chiplets (CCD) will then be stacked directly on the I/O die (IOD).

Zen 5 is expected for the first half of 2024 and Zen 6 for the second half of 2025.

[ad_2]

Source link